# Thermoelectric Module Standards

## 1. Purpose and Scope

This provides basic criteria for TE Technology Thermoelectric (Peltier) modules.

### 2. Handling

Improper handling of the Peltier module can cause inadvertent damage. Observe the following:

- Never handle the module by its wire leads such as to cause strain to the wire lead junction.

- The ceramics can be easily chipped; set the module down gently to avoid this.

- Do not set the module down in such a way that would cause a sharp edge to press onto a wire lead.

- If the module has output electrodes (which extend approximately 5 mm beyond the edge of the module, as identified by heat shrink tubing covering the solder joint), do not bend the wire within 9mm of the edge of the module. Use soft-nose pliers as required to prevent damage to the solder joint.

- If the module does not have output electrodes (as identified by an absence of heat shrink tubing and a solder joint within the perimeter of the module), do not bend within 4mm of the edge of the module. Use soft-nose pliers as required to prevent damage to the solder joint.

### 3. Substrates:

Some color variation or scuffing may exist in substrates.

Modules may have lot/date codes printed on the substrates.

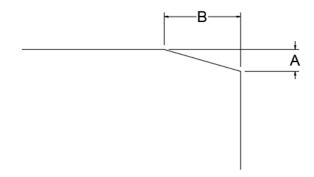

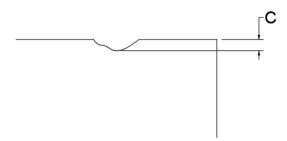

Cracks and chips along the edges of ceramics, while not desirable, are nonetheless permissible provided such chips do not exceed the following dimensions:

A: 1.3 mm maximum

B: 1.3 mm maximum

C: 0.7 mm maximum

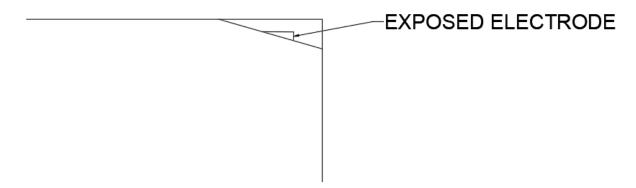

Modules that have cracks/chips which extend into areas above the copper electrodes must be rejected regardless of dimension:

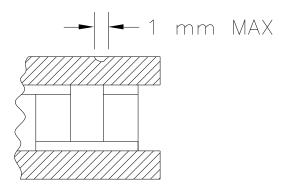

Pitting may occur on the ceramic surface. The maximum width in any direction shall not exceed 1 mm. Lapping and surface grinding marks shall not be considered a pit.

Modules with visible contamination or with residue that can be felt by the finger on the ceramic surface is to be rejected.

Semiconductor Elements:

- Semiconductor elements on the periphery of the module shall be aligned so that a minimum of 75% of the element footprint is located within the adjacent electrode.

- Damage to semiconductor elements on the periphery of the module shall not exceed more than 25% of the cross-sectional area of the element.

- Semiconductor elements on the periphery of the module that have a combination of partial misalignment and damage shall have a minimum of 75% of the element in connection to the adjacent electrode.

#### Wires:

- Wire insulation shall start within 2.5 mm of the substrate.

- On potted (perimeter-sealed) modules, the potting may break away from the wire insulation. Some exposed wire could occur.

- Wires may have nicked stranding, provided the number of nicks does not exceed the following limits:

o 7-strand wire: 2 nicks1 19-strand wire: 4 nicks<sup>1</sup>

<sup>1</sup>Nicks that are tinned with solder, do not expose the base metal (where wire is plated), or are less than 25% of the conductor diameter are not counted as a nick.

### Potting (perimeter sealing):

- Potting shall not extend above or below the mounting surfaces of the thermoelectric module.

- Modules potted with heat-cured potting (high-temperature potting) may exhibit a slight yellowing of the substrates.

- For single stage modules, potting may extend 1 mm beyond the perimeter of the thermoelectric module.

- Two stage modules may have potting extend more than 1mm beyond the perimeter of a module, especially in areas where an electrical jumper connecting the stages is covered in potting.

- Potting may have variations in color and texture, especially if the potting has been mechanically trimmed to meet dimensional requirements.

- The potting is not designed to adhere to the wire insulation and may pull away from the wire insulation.

Specific thermal and mechanical specifications are shown on the module data sheet. No other criteria expressed or implied.